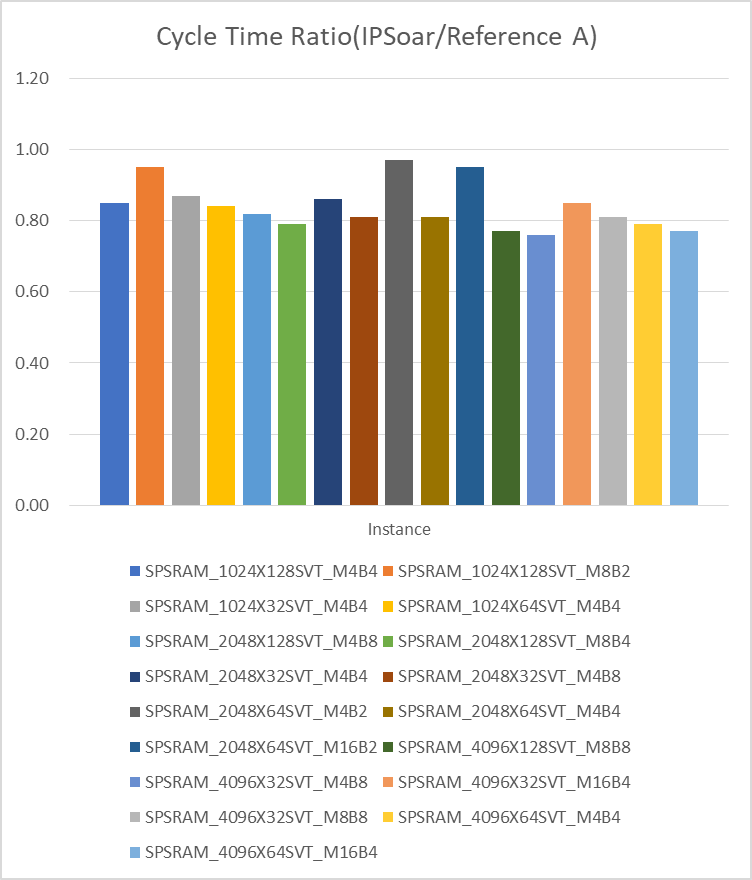

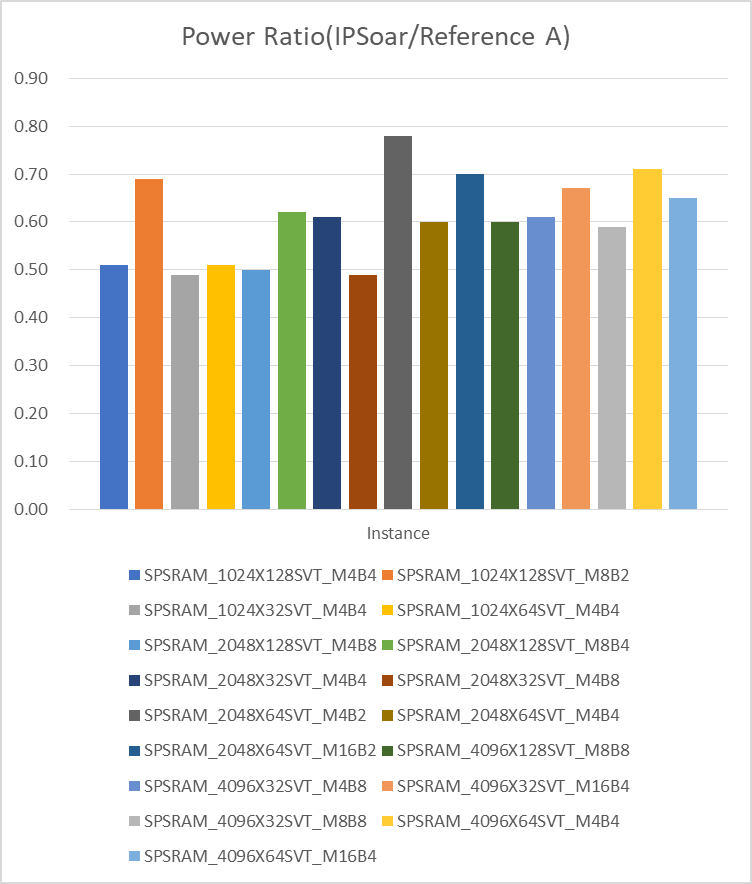

Ipsoar provide the most competitive memory compiler products in the semiconductor industry. Through full manual customization, ipsoar can meet customers' extreme demands in area, speed and power consumption, and help customers improve their product competitiveness.

Ipsoar memory compiler can reduce the static leakage current by 30 ~ 50% compared with the same period of last year; At the same time, it supports three low-power modes (nap, retention, power down) to meet the needs of customers in different low-power modes.

Ipsoar memory compilers provides industry-leading EDA models, including datasheet, Verilog behavior mode, liberty model, P & R model, DFT model, etc.

Ipsoar can provide products with advanced process node from 0.18um to 7nm.

Highlights:

Highlights:

● Process variation tolerance design technique to improve yield

● Reduce memory hard failure to improve yield by considering critical DFM rule

● Auto leakage control technique to reduce standby current

● Fully customized and optimized layout to get minimum area

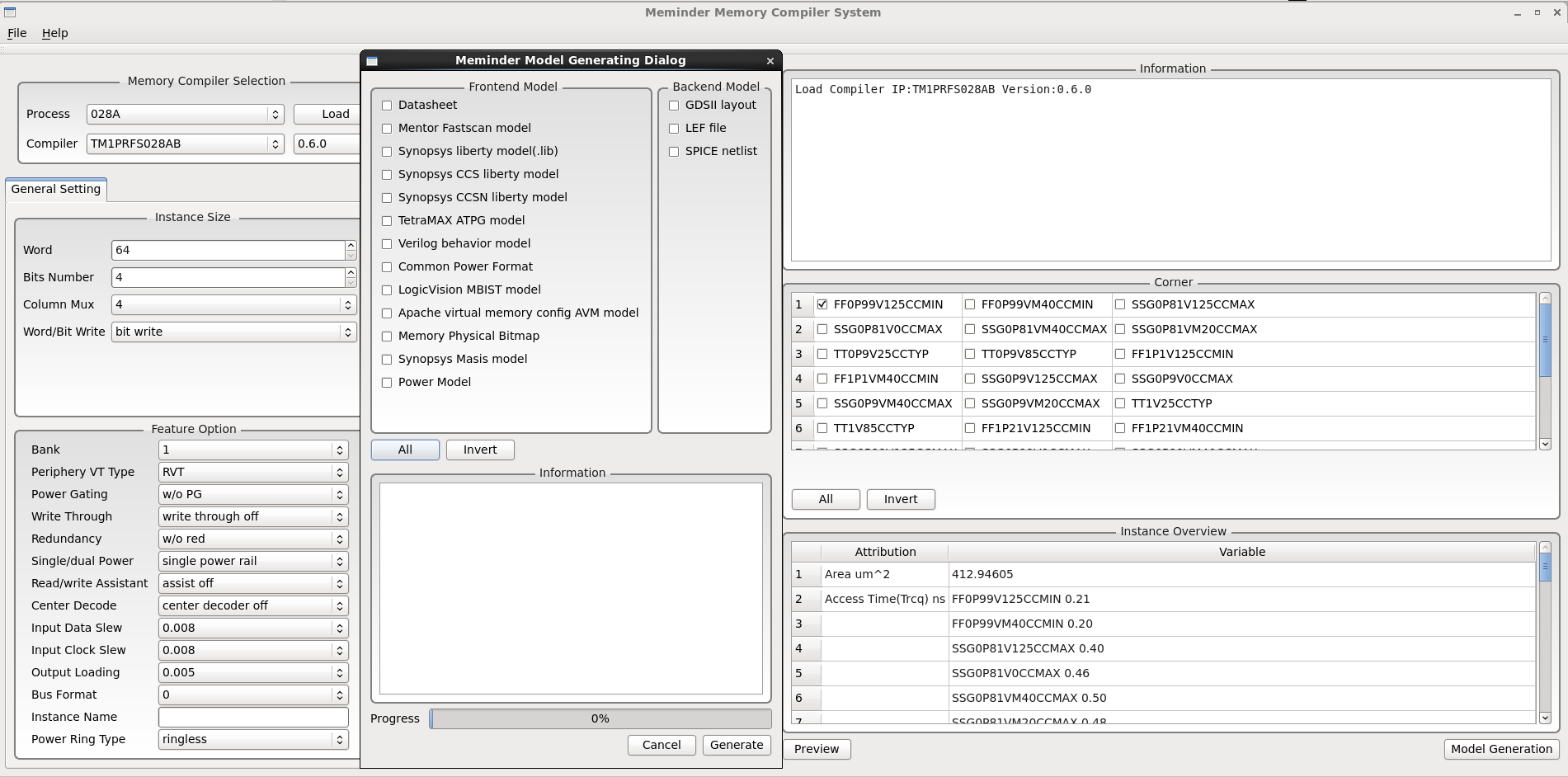

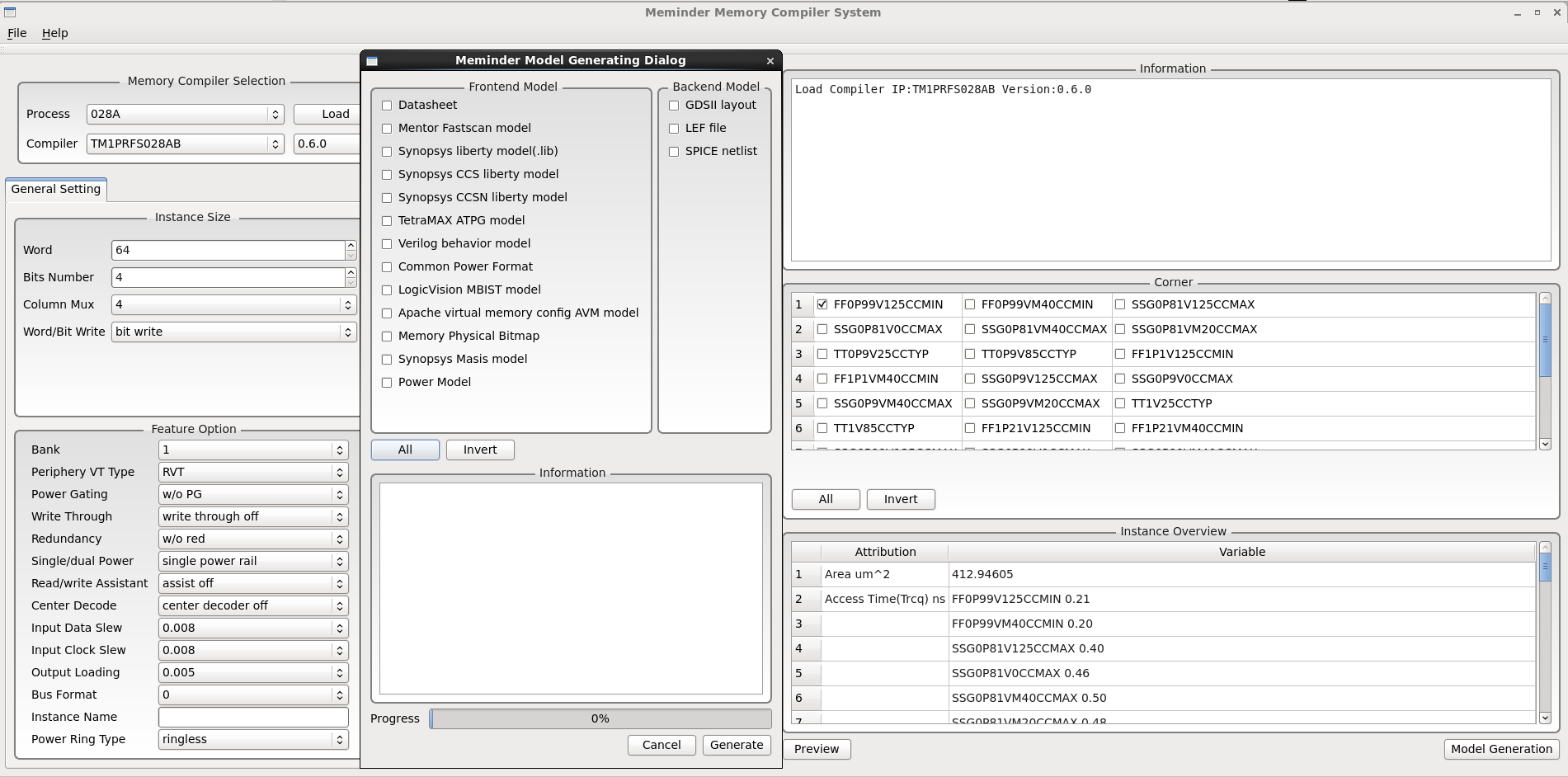

● Ultra faster memory compiler engine “Meminder” to generate memory instance rapidly

Deliverables:

Visual graph interface:

Deliverables:

● Verilog timing/simulation model

● VHDL timing/simulation model

● Spice-level netlist for LVS

● GDSII layout database

● Physical bitmap support

● Timing/Power/Noise liberty model

● P&R model

● Memory BIST model

Visual graph interface:

| Products | Memory Type |

|---|---|

| Memory Compiler | High Density Single Port SRAM |

| High Density One Port Register File | |

| High Speed Single Port SRAM | |

| High Speed One Port Register File | |

| Two Port Register File | |

| Two Port SRAM | |

| Dual Port SRAM | |

| Ultra high density two port register file (one clock) | |

| Ultra high density two port SRAM (one clock) | |

| Via ROM | |

| TCAM | |

| Special Multi-Port SRAM |